# ANALOG DEVICES

# Complete Quad, 16-Bit, High Accuracy, Serial Input, Bipolar Voltage Output DACs

# AD5764

#### FEATURES

Complete quad, 16-bit digital-to-analog converters (DACs) Programmable output range ±10 V, ±10.2564 V, or ±10.5263 V ±1 LSB maximum INL error, ±1 LSB maximum DNL error Low noise: 60 nV/√Hz Settling time: 10 µs maximum Integrated reference buffers Output control during power-up/brownout **Programmable short-circuit protection** Simultaneous updating via LDAC Asynchronous CLR to zero code **Digital offset and gain adjust** Logic output control pins DSP-/microcontroller-compatible serial interface Temperature range: -40°C to +85°C iCMOS process technology<sup>1</sup>

#### APPLICATIONS

Industrial automation Open-/closed-loop servo control Process control Data acquisition systems Automatic test equipment Automotive test and measurement High accuracy instrumentation

#### **GENERAL DESCRIPTION**

The AD5764 is a quad, 16-bit, serial input, bipolar voltage output DAC that operates from supply voltages of  $\pm 11.4$  V to  $\pm 16.5$  V. Nominal full-scale output range is  $\pm 10$  V. The AD5764 provides integrated output amplifiers, reference buffers, and proprietary power-up/power-down control circuitry. The part also features a digital I/O port, which is programmed via the serial interface. The part incorporates digital offset and gain adjust registers per channel.

The AD5764 is a high performance converter that offers guaranteed monotonicity, integral nonlinearity (INL) of  $\pm 1$  LSB, low noise, and 10 µs settling time. During power-up (when the supply voltages are changing), VOUTx is clamped to 0 V via a low impedance path.

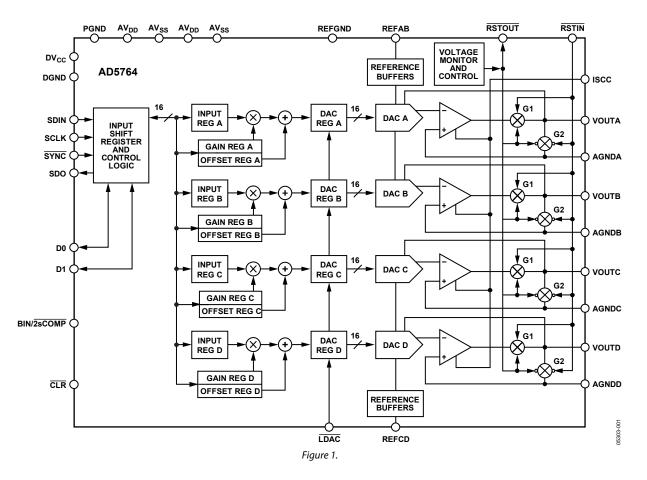

The AD5764 uses a serial interface that operates at clock rates of up to 30 MHz and is compatible with DSP and microcontroller interface standards. Double buffering allows the simultaneous updating of all DACs. The input coding is programmable to either twos complement or offset binary formats. The asynchronous clear function clears all DAC registers to either bipolar zero or zero scale depending on the coding used. The AD5764 is ideal for both closed-loop servo control and open-loop control applications. The AD5764 is available in a 32-lead TQFP, and offers guaranteed specifications over the  $-40^{\circ}$ C to  $+85^{\circ}$ C industrial temperature range. See Figure 1 for functional block diagram.

#### Table 1. Related Devices

| Part No. | Description                                                                    |

|----------|--------------------------------------------------------------------------------|

| AD5764R  | AD5764 with internal voltage reference                                         |

| AD5744   | Complete quad, 14-bit, high accuracy, serial input, bipolar voltage output DAC |

| AD5744R  | AD5744 with internal voltage reference                                         |

<sup>1</sup> For analog systems designers within industrial/instrumentation equipment OEMs who need high performance ICs at higher voltage levels, *i*CMOS<sup>®</sup> is a technology platform that enables the development of analog ICs capable of 30 V and operating at ±15 V supplies, allowing dramatic reductions in power consumption and package size, and increased ac and dc performance.

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006-2008

Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features 1                                    |

|-----------------------------------------------|

| Applications1                                 |

| General Description 1                         |

| Revision History 2                            |

| Functional Block Diagram 3                    |

| Specifications                                |

| AC Performance Characteristics                |

| Timing Characteristics                        |

| Absolute Maximum Ratings                      |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions10 |

| Typical Performance Characteristics           |

| Terminology 17                                |

| Theory of Operation                           |

| DAC Architecture                              |

| Reference Buffers                             |

| Reference Duriers                             |

| Serial Interface                              |

|                                               |

| Serial Interface                              |

#### **REVISION HISTORY**

#### 05/08—Rev. A to Rev. B

| Changes to Table Summary Statement, Specifications Section          | ion 4 |

|---------------------------------------------------------------------|-------|

| Changes to Power Requirements Parameter, Table 2 and                |       |

| Table Summary Statement                                             | 5     |

| Changes to t <sub>16</sub> Parameter, Table 4                       | 6     |

| Changes to Table 6                                                  | 10    |

| Changed $V_{SS}/V_{DD}$ to $AV_{SS}/AV_{DD}$ in Typical Performance |       |

| Characteristics Section                                             | 13    |

| Changes to Table 16                                                 | 22    |

| Changes to Table 18                                                 | 23    |

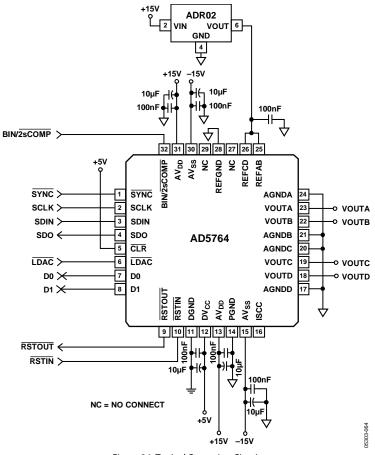

| Changes to Typical Operating Circuit Section                        | 28    |

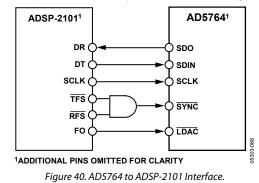

| Changes to AD5764 to ADSP-2101 Section                              | 29    |

| Changes to Ordering Guide                                           | 30    |

|                                                                     |       |

#### 1/07—Rev. 0 to Rev. A

| Changes to | Absolute Maximum     | Ratings | 10 |

|------------|----------------------|---------|----|

| Changes to | Figure 25 and Figure | 26      | 16 |

3/06—Revision 0: Initial Version

| Function Register                         | 21 |

|-------------------------------------------|----|

| Data Register                             | 21 |

| Coarse Gain Register                      | 21 |

| Fine Gain Register                        | 22 |

| Offset Register                           | 23 |

| Offset and Gain Adjustment Worked Example | 24 |

| Design Features                           | 25 |

| Analog Output Control                     | 25 |

| Digital Offset and Gain Control           | 25 |

| Programmable Short-Circuit Protection     | 25 |

| Digital I/O Port                          | 25 |

| Local Ground Offset Adjust                | 25 |

| Applications Information                  | 26 |

| Typical Operating Circuit                 | 26 |

| Layout Guidelines                         | 28 |

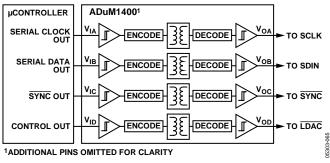

| Galvanically Isolated Interface           | 28 |

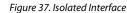

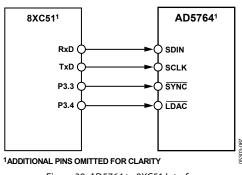

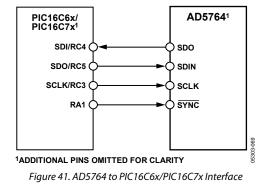

| Microprocessor Interfacing                | 28 |

| Evaluation Board                          | 29 |

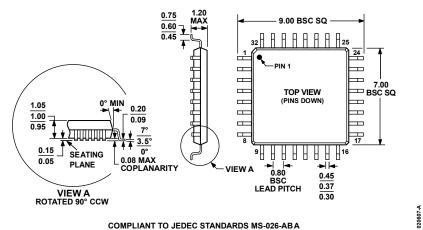

| Outline Dimensions                        | 30 |

| Ordering Guide                            | 30 |

### FUNCTIONAL BLOCK DIAGRAM

## **SPECIFICATIONS**

$AV_{DD} = 11.4 \text{ V}$  to 16.5 V,  $AV_{SS} = -11.4 \text{ V}$  to -16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;  $DV_{CC} = 2.7 \text{ V}$  to 5.25 V,  $R_{LOAD} = 10 \text{ k}\Omega$ ,  $C_L = 200 \text{ pF}$ . Temperature range:  $-40^{\circ}$ C to  $+85^{\circ}$ C; typical at  $+25^{\circ}$ C. Device functionality is guaranteed to  $+105^{\circ}$ C with degraded performance. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Parameter                                                 | A Grade  | B Grade  | C Grade  | Unit                      | Test Conditions/Comments                                            |

|-----------------------------------------------------------|----------|----------|----------|---------------------------|---------------------------------------------------------------------|

| ACCURACY                                                  |          |          |          |                           | Outputs unloaded                                                    |

| Resolution                                                | 16       | 16       | 16       | Bits                      |                                                                     |

| Relative Accuracy (INL)                                   | ±4       | ±2       | ±1       | LSB max                   |                                                                     |

| Differential Nonlinearity                                 | ±1       | ±1       | ±1       | LSB max                   | Guaranteed monotonic                                                |

| Bipolar Zero Error                                        | ±2       | ±2       | ±2       | mV max                    | At 25°C; error at other temperatures obtained using bipolar zero TC |

| Bipolar Zero Temperature<br>Coefficient (TC) <sup>1</sup> | ±2       | ±2       | ±2       | ppm FSR/°C max            |                                                                     |

| Zero-Scale Error                                          | ±2       | ±2       | ±2       | mV max                    | At 25°C; error at other temperatures obtained using zero-scale TC   |

| Zero-Scale TC <sup>1</sup>                                | ±2       | ±2       | ±2       | ppm FSR/°C max            |                                                                     |

| Gain Error                                                | ±0.02    | ±0.02    | ±0.02    | % FSR max                 | At 25°C; error at other temperatures obtained using gain TC         |

| Gain TC <sup>1</sup>                                      | ±2       | ±2       | ±2       | ppm FSR/°C max            |                                                                     |

| DC Crosstalk <sup>1</sup>                                 | 0.5      | 0.5      | 0.5      | LSB max                   |                                                                     |

| REFERENCE INPUT <sup>1</sup>                              |          |          |          |                           |                                                                     |

| Reference Input Voltage                                   | 5        | 5        | 5        | V nominal                 | ±1% for specified performance                                       |

| DC Input Impedance                                        | 1        | 1        | 1        | MΩ min                    | Typically 100 MΩ                                                    |

| Input Current                                             | ±10      | ±10      | ±10      | μA max                    | Typically ±30 nA                                                    |

| Reference Range                                           | 1 to 7   | 1 to 7   | 1 to 7   | V min to V max            |                                                                     |

| OUTPUT CHARACTERISTICS <sup>1</sup>                       |          |          |          |                           |                                                                     |

| Output Voltage Range <sup>2</sup>                         | ±10.5263 | ±10.5263 | ±10.5263 | V min to V max            | $AV_{DD}/AV_{SS} = \pm 11.4 V$ , REFIN = 5 V                        |

|                                                           | ±14      | ±14      | ±14      | V min to V max            | $AV_{DD}/AV_{SS} = \pm 16.5 V$ , REFIN = 7 V                        |

| Output Voltage Drift vs. Time                             | ±13      | ±13      | ±13      | ppm FSR/500<br>hours typ  |                                                                     |

|                                                           | ±15      | ±15      | ±15      | ppm FSR/1000<br>hours typ |                                                                     |

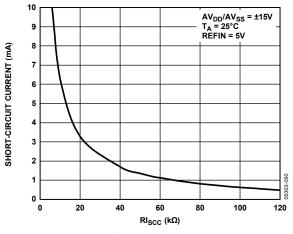

| Short-Circuit Current                                     | 10       | 10       | 10       | mA typ                    | $R_{ISCC} = 6 k\Omega$ , see Figure 31                              |

| Load Current                                              | ±1       | ±1       | ±1       | mA max                    | For specified performance                                           |

| Capacitive Load Stability                                 |          |          |          |                           |                                                                     |

| $R_{LOAD} = \infty$                                       | 200      | 200      | 200      | pF max                    |                                                                     |

| $R_{LOAD} = 10 \ k\Omega$                                 | 1000     | 1000     | 1000     | pF max                    |                                                                     |

| DC Output Impedance                                       | 0.3      | 0.3      | 0.3      | Ωmax                      |                                                                     |

| DIGITAL INPUTS <sup>1</sup>                               |          |          |          |                           | $DV_{CC} = 2.7$ V to 5.25 V, JEDEC compliant                        |

| Input High Voltage, V⊪                                    | 2        | 2        | 2        | V min                     |                                                                     |

| Input Low Voltage, V <sub>IL</sub>                        | 0.8      | 0.8      | 0.8      | V max                     |                                                                     |

| Input Current                                             | ±1       | ±1       | ±1       | μA max                    | Per pin                                                             |

| Pin Capacitance                                           | 10       | 10       | 10       | pF max                    | Per pin                                                             |

| Parameter                                  | A Grade                | B Grade           | C Grade                | Unit           | Test Conditions/Comments                           |

|--------------------------------------------|------------------------|-------------------|------------------------|----------------|----------------------------------------------------|

| DIGITAL OUTPUTS (D0, D1, SDO) <sup>1</sup> |                        |                   |                        |                |                                                    |

| Output Low Voltage                         | 0.4                    | 0.4               | 0.4                    | V max          | $DV_{CC} = 5 V \pm 5\%$ , sinking 200 $\mu$ A      |

| Output High Voltage                        | DVcc – 1               | DVcc – 1          | DVcc – 1               | V min          | $DV_{CC} = 5 V \pm 5\%$ , sourcing 200 $\mu$ A     |

| Output Low Voltage                         | 0.4                    | 0.4               | 0.4                    | V max          | $DV_{CC} = 2.7 V$ to 3.6 V, sinking 200 $\mu$ A    |

| Output High Voltage                        | DV <sub>CC</sub> – 0.5 | DVcc - 0.5        | DV <sub>cc</sub> – 0.5 | V min          | $DV_{CC} = 2.7 V$ to 3.6 V, sourcing 200 $\mu$ A   |

| High Impedance Leakage Current             | ±1                     | ±1                | ±1                     | μA max         | SDO only                                           |

| High Impedance Output<br>Capacitance       | 5                      | 5                 | 5                      | pF typ         | SDO only                                           |

| POWER REQUIREMENTS                         |                        |                   |                        |                |                                                    |

| AV <sub>DD</sub> /AV <sub>SS</sub>         | ±11.4 to<br>±16.5      | ±11.4 to<br>±16.5 | ±11.4 to<br>±16.5      | V min to V max |                                                    |

| DV <sub>cc</sub>                           | 2.7 to 5.25            | 2.7 to 5.25       | 2.7 to 5.25            | V min to V max |                                                    |

| Power Supply Sensitivity <sup>1</sup>      |                        |                   |                        |                |                                                    |

| $\Delta V_{OUT} / \Delta A V_{DD}$         | -85                    | -85               | -85                    | dB typ         |                                                    |

| Ald                                        | 3.5                    | 3.5               | 3.5                    | mA/channel max | Outputs unloaded                                   |

| Alss                                       | 2.75                   | 2.75              | 2.75                   | mA/channel max | Outputs unloaded                                   |

| DIcc                                       | 1.2                    | 1.2               | 1.2                    | mA max         | $V_{IH} = DV_{CC}, V_{IL} = DGND$ , 750 µA typical |

| Power Dissipation                          | 275                    | 275               | 275                    | mW typ         | ±12 V operation output unloaded                    |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> Output amplifier headroom requirement is 1.4 V minimum.

#### **AC PERFORMANCE CHARACTERISTICS**

$AV_{DD}$  = 11.4 V to 16.5 V,  $AV_{SS}$  = -11.4 V to -16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;  $DV_{CC}$  = 2.7 V to 5.25 V,  $R_{LOAD}$  = 10 k $\Omega$ ,  $C_L$  = 200 pF. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table | 3. |

|-------|----|

|       |    |

| Parameter                                                     | A Grade | B Grade | C Grade | Unit        | <b>Test Conditions/Comments</b>             |

|---------------------------------------------------------------|---------|---------|---------|-------------|---------------------------------------------|

| DYNAMIC PERFORMANCE <sup>1</sup>                              |         |         |         |             |                                             |

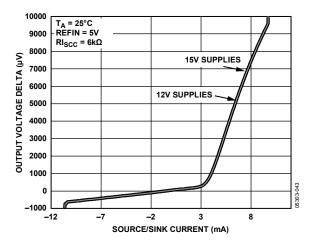

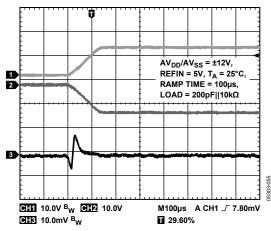

| Output Voltage Settling Time                                  | 8       | 8       | 8       | µs typ      | Full-scale step to ±1 LSB                   |

|                                                               | 10      | 10      | 10      | µs max      |                                             |

|                                                               | 2       | 2       | 2       | µs typ      | 512 LSB step settling                       |

| Slew Rate                                                     | 5       | 5       | 5       | V/µs typ    |                                             |

| Digital-to-Analog Glitch Energy                               | 8       | 8       | 8       | nV-sec typ  |                                             |

| Glitch Impulse Peak Amplitude                                 | 25      | 25      | 25      | mV max      |                                             |

| Channel-to-Channel Isolation                                  | 80      | 80      | 80      | dB typ      |                                             |

| DAC-to-DAC Crosstalk                                          | 8       | 8       | 8       | nV-sec typ  |                                             |

| Digital Crosstalk                                             | 2       | 2       | 2       | nV-sec typ  |                                             |

| Digital Feedthrough                                           | 2       | 2       | 2       | nV-sec typ  | Effect of input bus activity on DAC outputs |

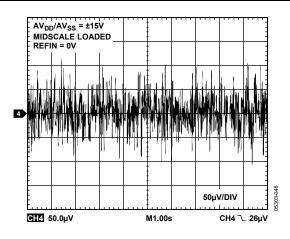

| Output Noise (0.1 Hz to 10 Hz)                                | 0.1     | 0.1     | 0.1     | LSB p-p typ |                                             |

| Output Noise (0.1 Hz to 100 kHz)                              | 45      | 45      | 45      | μV rms max  |                                             |

| 1/f Corner Frequency                                          | 1       | 1       | 1       | kHz typ     |                                             |

| Output Noise Spectral Density                                 | 60      | 60      | 60      | nV/√Hz typ  | Measured at 10 kHz                          |

| Complete System Output Noise Spectral<br>Density <sup>2</sup> | 80      | 80      | 80      | nV/√Hz typ  | Measured at 10 kHz                          |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> Includes noise contributions from integrated reference buffers, 16-bit DAC and output amplifier.

#### TIMING CHARACTERISTICS

$AV_{DD} = 11.4 \text{ V}$  to 16.5 V,  $AV_{SS} = -11.4 \text{ V}$  to -16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;  $DV_{CC} = 2.7 \text{ V}$  to 5.25 V,  $R_{LOAD} = 10 \text{ k}\Omega$ ,  $C_L = 200 \text{ pF}$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table 4.                        |                                              |        |                                                                                                   |

|---------------------------------|----------------------------------------------|--------|---------------------------------------------------------------------------------------------------|

| Parameter <sup>1, 2, 3</sup>    | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                                       |

| t <sub>1</sub>                  | 33                                           | ns min | SCLK cycle time                                                                                   |

| t <sub>2</sub>                  | 13                                           | ns min | SCLK high time                                                                                    |

| t <sub>3</sub>                  | 13                                           | ns min | SCLK low time                                                                                     |

| t <sub>4</sub>                  | 13                                           | ns min | SYNC falling edge to SCLK falling edge setup time                                                 |

| t5 <sup>4</sup>                 | 13                                           | ns min | 24 <sup>th</sup> SCLK falling edge to SYNC rising edge                                            |

| t <sub>6</sub>                  | 40                                           | ns min | Minimum SYNC high time                                                                            |

| t7                              | 2                                            | ns min | Data setup time                                                                                   |

| t <sub>8</sub>                  | 5                                            | ns min | Data hold time                                                                                    |

| t9                              | 1.4                                          | µs min | SYNC rising edge to LDAC falling edge (all DACs updated)                                          |

|                                 | 400                                          | ns min | SYNC rising edge to LDAC falling edge (single DAC updated)                                        |

| t <sub>10</sub>                 | 10                                           | ns min | LDAC pulse width low                                                                              |

| t11                             | 500                                          | ns max | LDAC falling edge to DAC output response time                                                     |

| t <sub>12</sub>                 | 10                                           | µs max | DAC output settling time                                                                          |

| t <sub>13</sub>                 | 10                                           | ns min | CLR pulse width low                                                                               |

| t <sub>14</sub>                 | 2                                            | µs max | CLR pulse activation time                                                                         |

| t <sub>15</sub> <sup>5, 6</sup> | 25                                           | ns max | SCLK rising edge to SDO valid                                                                     |

| t <sub>16</sub>                 | 13                                           | ns min | SYNC rising edge to SCLK falling edge                                                             |

| t <sub>17</sub>                 | 2                                            | µs min | $\overline{\text{SYNC}}$ rising edge to DAC output response time ( $\overline{\text{LDAC}} = 0$ ) |

| t <sub>18</sub>                 | 170                                          | ns min | LDAC falling edge to SYNC rising edge                                                             |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of DV<sub>cc</sub>) and timed from a voltage level of 1.2 V.

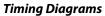

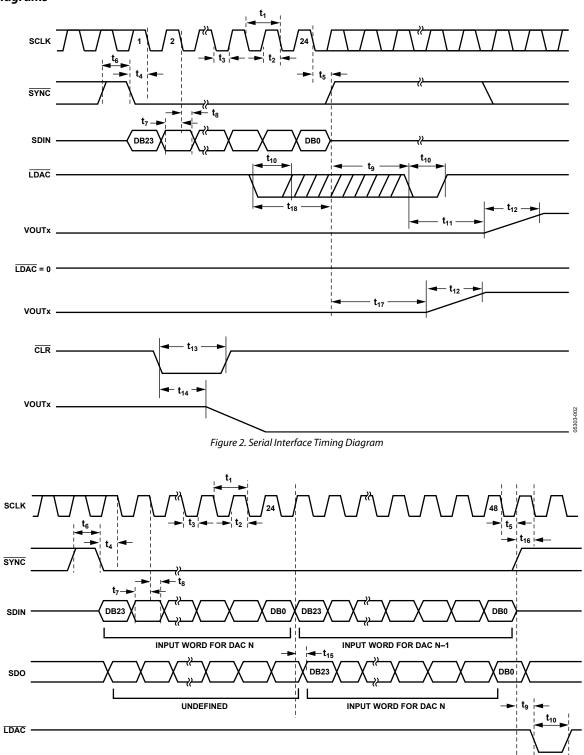

<sup>3</sup> See Figure 2, Figure 3, and Figure 4.

<sup>4</sup> Standalone mode only.

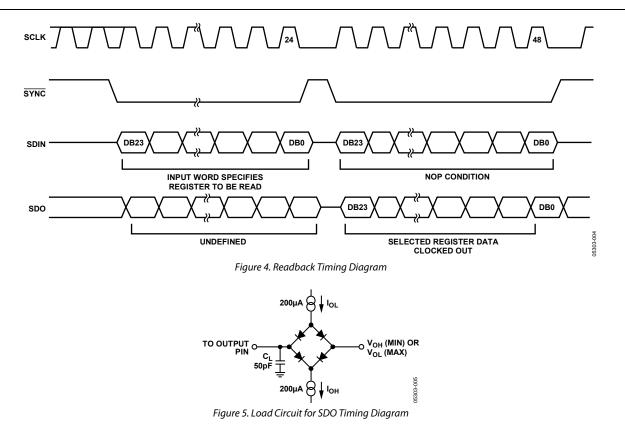

<sup>5</sup> Measured with the load circuit of Figure 5.

<sup>6</sup> Daisy-chain mode only.

Figure 3. Daisy-Chain Timing Diagram

# ABSOLUTE MAXIMUM RATINGS

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

#### Table 5.

| Parameter                              | Rating                                                           |

|----------------------------------------|------------------------------------------------------------------|

|                                        | -0.3 V to $+17$ V                                                |

| AV <sub>DD</sub> to AGNDx, DGND        |                                                                  |

| AV <sub>ss</sub> to AGNDx, DGND        | +0.3 V to –17 V                                                  |

| DVcc to DGND                           | –0.3 V to +7 V                                                   |

| Digital Inputs to DGND                 | -0.3 V to DV <sub>CC</sub> + 0.3 V or 7 V<br>(whichever is less) |

| Digital Outputs to DGND                | -0.3 V to DV <sub>CC</sub> + 0.3 V                               |

| REFIN to AGNDx, PGND                   | -0.3 V to AV <sub>DD</sub> + 0.3 V                               |

| VOUTA, VOUTB, VOUTC, VOUTD to<br>AGNDx | AV <sub>ss</sub> to AV <sub>DD</sub>                             |

| AGNDx to DGND                          | –0.3 V to +0.3 V                                                 |

| Operating Temperature Range            |                                                                  |

| Industrial                             | –40°C to +85°C                                                   |

| Storage Temperature Range              | –65°C to +150°C                                                  |

| Junction Temperature (TJ max)          | 150°C                                                            |

| 32-Lead TQFP                           |                                                                  |

| $\theta_{JA}$ Thermal Impedance        | 65°C/W                                                           |

| θ <sub>JC</sub> Thermal Impedance      | 12°C/W                                                           |

| Lead Temperature                       | JEDEC Industry Standard                                          |

| Soldering                              | J-STD-020                                                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

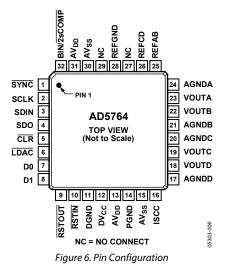

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 6. Pin Function Descriptions**

| Pin No.        | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | SYNC             | Active Low Input. This is the frame synchronization signal for the serial interface. While SYNC is low,                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |                  | data is transferred in on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2              | SCLK             | Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 30 MHz.                                                                                                                                                                                                                                                                                                                                                                    |

| 3              | SDIN             | Serial Data Input. Data must be valid on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4              | SDO              | Serial Data Output. Used to clock data from the serial register in daisy-chain or readback mode.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5 <sup>1</sup> | CLR              | Negative Edge Triggered Input. Asserting this pin sets the DAC registers to 0x0000.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6              | IDAC             | Load DAC. Logic input. This is used to update the DAC registers and consequently the analog outputs.<br>When tied permanently low, the addressed DAC register is updated on the rising edge of SYNC. If<br>LDAC is held high during the write cycle, the DAC input register is updated but the output update is<br>held off until the falling edge of LDAC. In this mode, all analog outputs can be updated simulta-<br>neously on the falling edge of LDAC. The LDAC pin must not be left unconnected. |

| 7, 8           | D0, D1           | Digital I/O port. The user can set up these pins as inputs or outputs that are configurable and readable over the serial interface. When configured as inputs, these pins have weak internal pull-ups to DV <sub>cc</sub> . When programmed as outputs, D0 and D1 are referenced by DV <sub>cc</sub> and DGND.                                                                                                                                                                                          |

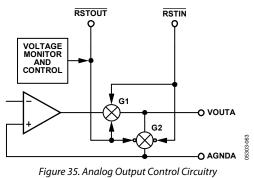

| 9              | RSTOUT           | Reset Logic Output. This is the output from the on-chip voltage monitor used in the reset circuit. If desired, it can be used to control other system components.                                                                                                                                                                                                                                                                                                                                       |

| 10             | RSTIN            | Reset Logic Input. This input allows external access to the internal reset logic. Applying a Logic 0 to this input clamps the DAC outputs to 0 V. In normal operation, RSTIN should be tied to Logic 1. Register values remain unchanged.                                                                                                                                                                                                                                                               |

| 11             | DGND             | Digital Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12             | DVcc             | Digital Supply Pin. Voltage ranges from 2.7 V to 5.25 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13, 31         | AV <sub>DD</sub> | Positive Analog Supply Pins. Voltage ranges from 11.4 V to 16.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14             | PGND             | Ground Reference Point for Analog Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15, 30         | AVss             | Negative Analog Supply Pins. Voltage ranges from -11.4 V to -16.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16             | ISCC             | Resistor Connection for Pin Programmable Short-Circuit Current. This pin is used in association with an optional external resistor to AGND to program the short-circuit current of the output amplifiers. Refer to the Design Features section for further details.                                                                                                                                                                                                                                     |

| 17             | AGNDD            | Ground Reference Pin for DAC D Output Amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18             | VOUTD            | Analog Output Voltage of DAC D. Buffered output with a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                                                                                                                                                                                                                                                                                                |

| 19             | VOUTC            | Analog Output Voltage of DAC C. Buffered output with a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                                                                                                                                                                                                                                                                                                |

| 20             | AGNDC            | Ground Reference Pin for DAC C Output Amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21             | AGNDB            | Ground Reference Pin for DAC B Output Amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                            |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22      | VOUTB      | Analog Output Voltage of DAC B. Buffered output with a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                               |

| 23      | VOUTA      | Analog Output Voltage of DAC A. Buffered output with a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                               |

| 24      | AGNDA      | Ground Reference Pin for DAC A Output Amplifier.                                                                                                                                                                                       |

| 25      | REFAB      | External Reference Voltage Input for Channel A and Channel B. Reference input range is 1 V to 7 V; programs the full-scale output voltage. REFIN = 5 V for specified performance.                                                      |

| 26      | REFCD      | External Reference Voltage Input for Channel C and Channel D. Reference input range is 1 V to 7 V; programs the full-scale output voltage. REFIN = 5 V for specified performance.                                                      |

| 27, 29  | NC         | No Connect.                                                                                                                                                                                                                            |

| 28      | REFGND     | Reference Ground Return for the Reference Generator and Buffers.                                                                                                                                                                       |

| 32      | BIN/2sCOMP | Determines the DAC Coding. This pin should be hardwired to either DV <sub>CC</sub> or DGND. When hardwired to DV <sub>CC</sub> , input coding is offset binary. When hardwired to DGND, input coding is twos complement (see Table 7). |

<sup>1</sup> Internal pull-up device on this logic input. Therefore, it can be left floating and defaults to a Logic 1 condition.

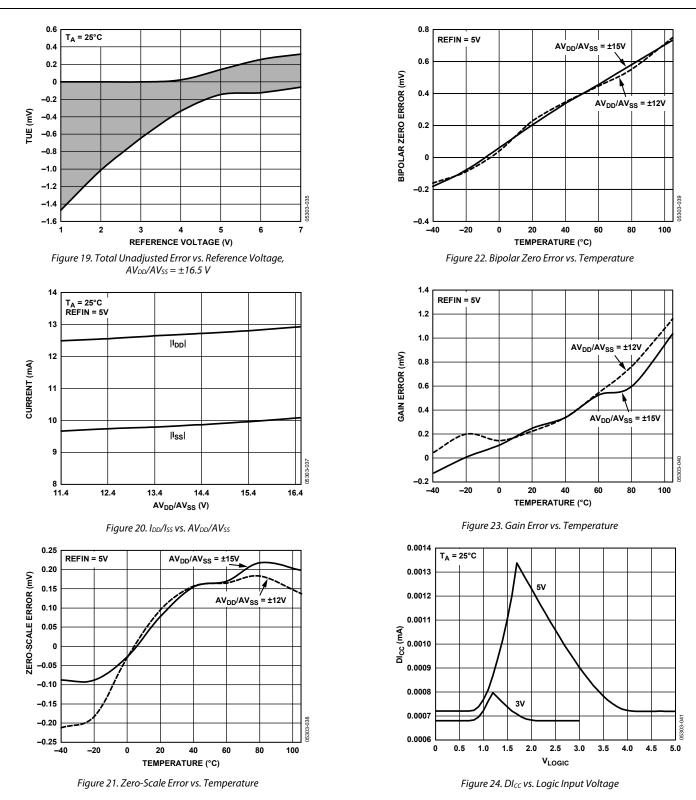

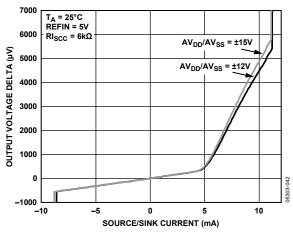

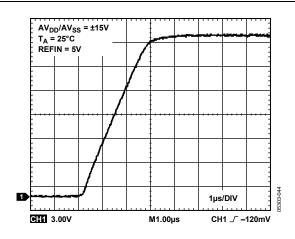

Figure 25. Source and Sink Capability of Output Amplifier with Positive Full Scale Loaded

Figure 26. Source and Sink Capability of Output Amplifier with Negative Full Scale Loaded

Figure 27. Full-Scale Settling Time

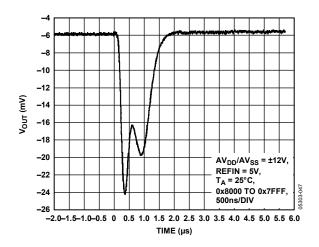

Figure 28. Major Code Transition Glitch Energy,  $AV_{DD}/AV_{SS} = \pm 12 V$

Figure 29. Peak-to-Peak Noise (100 kHz Bandwidth)

Figure 30. VOUT vs. AVDD/AVSS on Power-Up

Figure 31. Short-Circuit Current vs. RIscc

# TERMINOLOGY

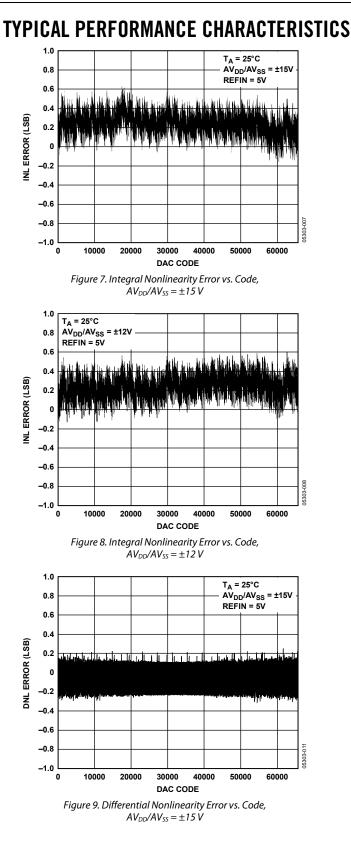

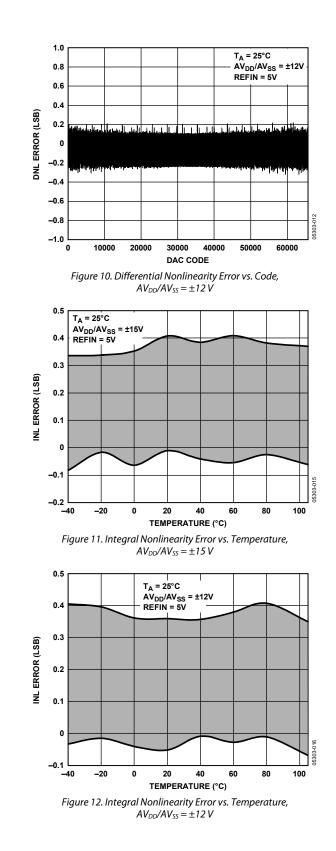

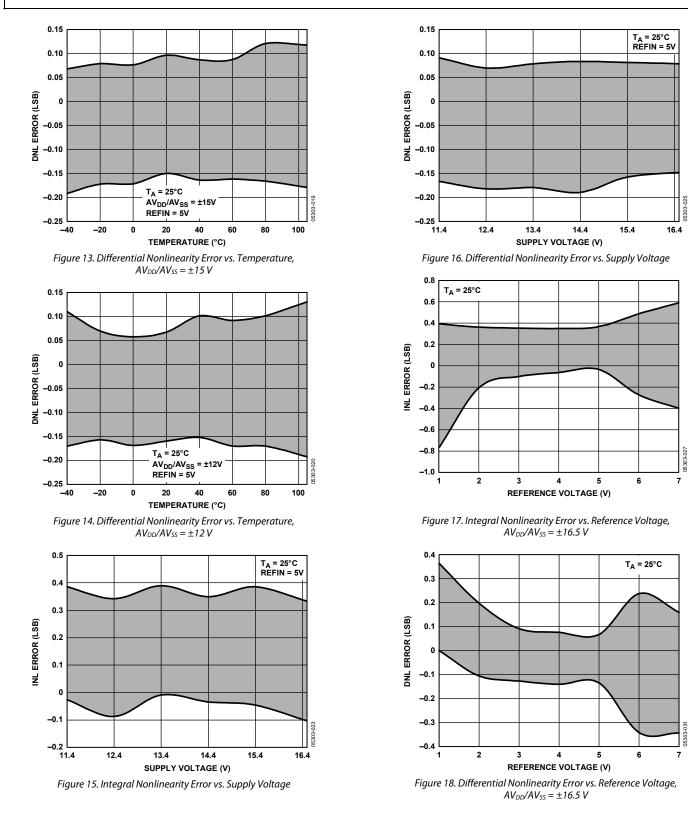

#### Relative Accuracy or Integral Nonlinearity (INL)

For the DAC, relative accuracy or integral nonlinearity (INL) is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A typical INL vs. code plot can be seen in Figure 7.

#### Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm$ 1 LSB maximum ensures monotonicity. This DAC is guaranteed monotonic. A typical DNL vs. code plot can be seen in Figure 9.

#### Monotonicity

A DAC is monotonic if the output either increases or remains constant for increasing digital input code. The AD5764 is monotonic over its full operating temperature range.

#### **Bipolar Zero Error**

Bipolar zero error is the deviation of the analog output from the ideal half-scale output of 0 V when the DAC register is loaded with 0x8000 (offset binary coding) or 0x0000 (twos complement coding). A plot of bipolar zero error vs. temperature can be seen in Figure 22.

#### **Bipolar Zero Temperature Coefficient (TC)**

Bipolar zero TC is the measure of the change in the bipolar zero error with a change in temperature. It is expressed in ppm FSR/°C.

#### **Full-Scale Error**

Full-scale error is a measure of the output error when full-scale code is loaded to the DAC register. Ideally, the output voltage should be  $2 \times V_{REF} - 1$  LSB. Full-scale error is expressed in percentage of full-scale range.

#### Negative Full-Scale Error/Zero-Scale Error

Negative full-scale error is the error in the DAC output voltage when 0x0000 (offset binary coding) or 0x8000 (twos complement coding) is loaded to the DAC register. Ideally, the output voltage should be  $-2 \times V_{REF}$ . A plot of zero-scale error vs. temperature can be seen in Figure 21.

#### **Output Voltage Settling Time**

Output voltage settling time is the amount of time it takes for the output to settle to a specified level for a full-scale input change.

#### Slew Rate

The slew rate of a device is a limitation in the rate of change of the output voltage. The output slewing speed of a voltage-output DAC is usually limited by the slew rate of the amplifier used at its output. Slew rate is measured from 10% to 90% of the output signal and is given in  $V/\mu s$ .

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal, expressed as a percentage of the full-scale range. A plot of gain error vs. temperature can be seen in Figure 23.

#### **Total Unadjusted Error**

Total unadjusted error (TUE) is a measure of the output error considering all the various errors. A plot of total unadjusted error vs. reference can be seen in Figure 19.

#### Zero-Scale Error Temperature Coefficient (TC)

Zero-scale error TC is a measure of the change in zero-scale error with a change in temperature. Zero-scale error TC is expressed in ppm FSR/°C.

#### Gain Error Temperature Coefficient (TC)

Gain error TC is a measure of the change in gain error with changes in temperature. Gain error TC is expressed in (ppm of FSR)/°C.

#### Digital-to-Analog Glitch Energy

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-secs and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x7FFF to 0x8000), see Figure 28.

#### **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC but is measured when the DAC output is not updated. It is specified in nV-secs and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s, and vice versa.

#### **Power Supply Sensitivity**

Power supply sensitivity indicates how the output of the DAC is affected by changes in the power supply voltage.

#### DC Crosstalk

DC crosstalk is the dc change in the output level of one DAC in response to a change in the output of another DAC. It is measured with a full-scale output change on one DAC while monitoring another DAC, and is expressed in LSBs.

#### DAC-to-DAC Crosstalk

DAC-to-DAC crosstalk is the glitch impulse transferred to the output of one DAC due to a digital code change and subsequent output change of another DAC. This includes both digital and analog crosstalk. It is measured by loading one of the DACs with a full-scale code change (all 0s to all 1s and vice versa) with  $\overline{\text{LDAC}}$  low and monitoring the output of another DAC. The energy of the glitch is expressed in nV-sec.

#### **Channel-to-Channel Isolation**

Channel-to-channel isolation is the ratio of the amplitude of the signal at the output of one DAC to a sine wave on the reference input of another DAC. It is measured in dB.

#### **Digital Crosstalk**

Digital crosstalk is a measure of the impulse injected into the analog output of one DAC from the digital inputs of another DAC but is measured when the DAC output is not updated. It is specified in nV-secs and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s, and vice versa.

# THEORY OF OPERATION

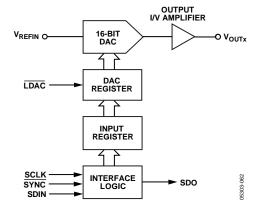

The AD5764 is a quad, 16-bit, serial input, bipolar voltage output DAC and operates from supply voltages of  $\pm 11.4$  V to  $\pm 16.5$  V and has a buffered output voltage of up to  $\pm 10.5263$  V. Data is written to the AD5764 in a 24-bit word format, via a 3-wire serial interface. The device also offers an SDO pin, which is available for daisy-chaining or readback.

The AD5764 incorporates a power-on reset circuit, which ensures that the DAC registers power up loaded with 0x0000. The AD5764 features a digital I/O port that can be programmed via the serial interface, on-chip reference buffers and per channel digital gain, and offset registers.

#### DAC ARCHITECTURE

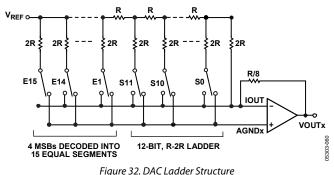

The DAC architecture of the AD5764 consists of a 16-bit current mode segmented R-2R DAC. The simplified circuit diagram for the DAC section is shown in Figure 32.

The four MSBs of the 16-bit data word are decoded to drive 15 switches, E1 to E15. Each of these switches connects one of the 15 matched resistors to either AGNDx or IOUT. The remaining 12 bits of the data-word drive Switch S0 to Switch S11 of the 12-bit R-2R ladder network.

#### **REFERENCE BUFFERS**

The AD5764 operates with an external reference. The reference inputs (REFAB and REFCD) have an input range up to 7 V. This input voltage is used to provide a buffered positive and negative reference for the DAC cores. The positive reference is given by

$+V_{REF} = 2 \times V_{REF}$

The negative reference to the DAC cores is given by

$$-V_{REF} = -2 \times V_{REF}$$

These positive and negative reference voltages (along with the gain register values) define the output ranges of the DACs.

#### SERIAL INTERFACE

The AD5764 is controlled over a versatile 3-wire serial interface that operates at clock rates of up to 30 MHz and is compatible with SPI,  $QSPI^{II}$ , MICROWIRE<sup>III</sup>, and DSP standards.

#### Input Shift Register

The input shift register is 24 bits wide. Data is loaded into the device MSB first as a 24-bit word under the control of a serial clock input, SCLK. The input register consists of a read/write bit, three register select bits, three DAC address bits, and 16 data bits, as shown in Table 8. The timing diagram for this operation is shown in Figure 2.

Upon power-up, the DAC registers are loaded with zero code (0x0000), and the outputs are clamped to 0 V via a low impedance path. The outputs can be updated with the zero code value at this time by asserting either LDAC or CLR. The corresponding output voltage depends on the state of the BIN/2sCOMP pin. If the BIN/2sCOMP pin is tied to DGND, the data coding is twos complement, and the outputs update to 0 V. If the BIN/2sCOMP pin is tied to DV<sub>CC</sub>, the data coding is offset binary, and the outputs update to negative full scale. To have the outputs power-up with zero code loaded to the outputs, the CLR pin should be held low during power-up.

#### **Standalone Operation**

The serial interface works with both a continuous and noncontinuous serial clock. A continuous SCLK source can only be used if SYNC is held low for the correct number of clock cycles. In gated clock mode, a burst clock containing the exact number of clock cycles must be used and SYNC must be taken high after the final clock to latch the data. The first falling edge of SYNC starts the write cycle. Exactly 24 falling clock edges must be applied to SCLK before SYNC is brought high again. If SYNC is brought high before the 24th falling SCLK edge, the data written is invalid. If more than 24 falling SCLK edges are applied before SYNC is brought high, the input data is also invalid. The input register addressed is updated on the rising edge of SYNC. For another serial transfer to take place, SYNC must be brought low again. After the end of the serial data transfer, data is automatically transferred from the input shift register to the addressed register.

When the data has been transferred into the chosen register of the addressed DAC, all DAC registers and outputs can be updated by taking LDAC low.

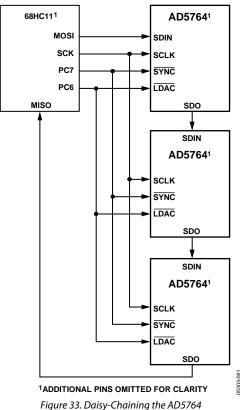

#### **Daisy-Chain Operation**

For systems that contain several devices, the SDO pin can be used to daisy-chain several devices together. This daisy-chain mode can be useful in system diagnostics and in reducing the number of serial interface lines. The first falling edge of SYNC starts the write cycle. The SCLK is continuously applied to the input shift register when SYNC is low. If more than 24 clock pulses are applied, the data ripples out of the shift register and appears on the SDO line. This data is clocked out on the rising edge of SCLK and is valid on the falling edge. By connecting the SDO of the first device to the SDIN input of the next device in the chain, a multidevice interface is constructed. Each device in the system requires 24 clock pulses. Therefore, the total number of clock cycles must equal 24N, where N is the total number of AD5764 devices in the chain. When the serial transfer to all devices is complete, SYNC is taken high. This latches the input data in each device in the daisy chain and prevents any further data from being clocked into the input shift register. The serial clock can be a continuous or a gated clock.

A continuous SCLK source can only be used if SYNC is held low for the correct number of clock cycles. In gated clock mode, a burst clock containing the exact number of clock cycles must be used, and SYNC must be taken high after the final clock to latch the data.

#### **Readback Operation**

Before a readback operation is initiated, the SDO pin must be enabled by writing to the function register and clearing the SDO disable bit; this bit is cleared by default. Readback mode is invoked by setting the  $R/\overline{W}$  bit = 1 in the serial input register write. With  $R/\overline{W} = 1$ , Bit A2 to Bit A0, in association with Bit REG2, Bit REG1, and Bit REG0, select the register to be read. The remaining data bits in the write sequence are don't cares. During the next SPI write, the data appearing on the SDO output contain the data from the previously addressed register. For a read of a single register, the NOP command can be used in clocking out the data from the selected register on SDO. The readback diagram in Figure 4 shows the readback sequence. For example, to read back the fine gain register of Channel A on the AD5764, implement the following:

- 1. Write 0xA0XXXX to the AD5764 input register. This configures the AD5764 for read mode with the fine gain register of Channel A selected. Note that all the data bits, DB15 to DB0, are don't cares.

- 2. Follow this with a second write, an NOP condition, 0x00XXXX. During this write, the data from the fine gain register is clocked out on the SDO line, that is, data clocked out contain the data from the fine gain register in Bit DB5 to Bit DB0.

#### SIMULTANEOUS UPDATING VIA LDAC

Depending on the status of both  $\overline{\text{SYNC}}$  and  $\overline{\text{LDAC}}$ , and after data has been transferred into the input register of the DACs, there are two ways in which the DAC registers and DAC outputs can be updated.

#### Individual DAC Updating

In this mode,  $\overline{\text{LDAC}}$  is held low while data is being clocked into the input shift register. The addressed DAC output is updated on the rising edge of SYNC.

#### Simultaneous Updating of All DACs

In this mode,  $\overline{\text{LDAC}}$  is held high while data is being clocked into the input shift register. All DAC outputs are updated by taking  $\overline{\text{LDAC}}$  low any time after  $\overline{\text{SYNC}}$  has been taken high. The update now occurs on the falling edge of  $\overline{\text{LDAC}}$ .

Figure 34. Simplified Serial Interface of Input Loading Circuitry for One DAC Channel

#### **TRANSFER FUNCTION**

Table 7 shows the ideal input code to output voltage relationship for the AD5764 for both offset binary and twos complement data coding.

#### Table 7. Ideal Output Voltage to Input Code Relationship

|        | Digit     | al Input  |        |                                       |

|--------|-----------|-----------|--------|---------------------------------------|

| Off    | set Binaı | y Data Co | oding  | Analog Output                         |

| MSB    |           |           | LSB    | VOUTx                                 |

| 1111   | 1111      | 1111      | 1111   | +2 V <sub>REF</sub> × (32,767/32,768) |

| 1000   | 0000      | 0000      | 0001   | $+2 V_{REF} \times (1/32,768)$        |

| 1000   | 0000      | 0000      | 0000   | 0 V                                   |

| 0111   | 1111      | 1111      | 1111   | $-2 V_{REF} \times (1/32,768)$        |

| 0000   | 0000      | 0000      | 0000   | $-2 V_{REF} \times (32,767/32,768)$   |

| Twos ( | Complen   | nent Data | Coding |                                       |

| MSB    |           |           | LSB    | VOUTx                                 |

| 0111   | 1111      | 1111      | 1111   | $+2 V_{REF} \times (32,767/32,768)$   |

| 0000   | 0000      | 0000      | 0001   | $+2 V_{REF} \times (1/32,768)$        |

| 0000   | 0000      | 0000      | 0000   | 0 V                                   |

| 1111   | 1111      | 1111      | 1111   | $-2 V_{REF} \times (1/32,768)$        |

| 1000   | 0000      | 0000      | 0000   | $-2 V_{REF} \times (32,767/32,768)$   |

The output voltage expression for the AD5764 is given by

$$V_{OUT} = -2 \times V_{REFIN} + 4 \times V_{REFIN} \left[ \frac{D}{65,536} \right]$$

where:

*D* is the decimal equivalent of the code loaded to the DAC.  $V_{REFIN}$  is the reference voltage applied at the REFAB/REFCD pins.

#### **ASYNCHRONOUS CLEAR** (CLR)

CLR is a negative edge triggered clear that allows the outputs to be cleared to either 0 V (twos complement coding) or negative full scale (offset binary coding). It is necessary to maintain CLR low for a minimum amount of time (see Figure 2) for the operation to complete. When the CLR signal is returned high, the output remains at the cleared value until a new value is programmed. If at power-on, CLR is at 0 V, then all DAC outputs are updated with the clear value. A clear can also be initiated through software by writing the command 0x04XXXX to the AD5764.

#### Table 8. Input Register Bit Map

| MSB  |      |      |      |      |      |      |      | LSB      |

|------|------|------|------|------|------|------|------|----------|

| DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15:DB0 |

| R/W  | 0    | REG2 | REG1 | REG0 | A2   | A1   | A0   | DATA     |

| Bit              | Descript                                                                                                                                                           | Description |      |                      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|----------------------|--|--|--|--|--|

| R/W              | Indicates a read from or a write to the addressed register.                                                                                                        |             |      |                      |  |  |  |  |  |

| REG2, REG1, REG0 | Used in association with the address bits to determine if a read or write operation is to the data register, offset register, gain register, or function register. |             |      |                      |  |  |  |  |  |

|                  | REG2                                                                                                                                                               | REG1        | REG0 | Function             |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 0           | 0    | Function Register    |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 1           | 0    | Data Register        |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 1           | 1    | Coarse Gain Register |  |  |  |  |  |

|                  | 1                                                                                                                                                                  | 0           | 0    | Fine Gain Register   |  |  |  |  |  |

|                  | 1                                                                                                                                                                  | 0           | 1    | Offset Register      |  |  |  |  |  |

| A2, A1, A0       | These bits are used to decode the DAC channels.                                                                                                                    |             |      |                      |  |  |  |  |  |

|                  | A2                                                                                                                                                                 | A1          | A0   | Channel Address      |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 0           | 0    | DAC A                |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 0           | 1    | DAC B                |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 1           | 0    | DACC                 |  |  |  |  |  |

|                  | 0                                                                                                                                                                  | 1           | 1    | DAC D                |  |  |  |  |  |

|                  | 1                                                                                                                                                                  | 0           | 0    | All DACs             |  |  |  |  |  |

| D15:D0           | Data Bits                                                                                                                                                          |             |      |                      |  |  |  |  |  |

#### **Table 9. Input Register Bit Functions**

#### **FUNCTION REGISTER**

The function register is addressed by setting the three REG bits to 000. The values written to the address bits and the data bits determine the function addressed. The functions available via the function register are outlined in Table 10 and Table 11.

| REG2 | REG1 | REG0 | A2 | A1 | A0 | DB15:DB6   | DB5                                | DB4             | DB3          | DB2             | DB1         | DB0            |

|------|------|------|----|----|----|------------|------------------------------------|-----------------|--------------|-----------------|-------------|----------------|

| 0    | 0    | 0    | 0  | 0  | 0  |            |                                    | NOP, Data :     | = Don't Care | 5               |             |                |

| 0    | 0    | 0    | 0  | 0  | 1  | Don't Care | Local-<br>Ground-<br>Offset Adjust | D1<br>Direction | D1<br>Value  | D0<br>Direction | D0<br>Value | SDO<br>Disable |

| 0    | 0    | 0    | 1  | 0  | 0  |            | CLR, Data = Don't Care             |                 |              |                 |             |                |

| 0    | 0    | 0    | 1  | 0  | 1  |            |                                    | LOAD, Data      | = Don't Ca   | re              |             |                |

#### Table 10. Function Register Options

#### Table 11. Explanation of Function Register Options

| Option                         | Description                                                                                                                                                                                                                                                                                                            |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP                            | No operation instruction used in readback operations.                                                                                                                                                                                                                                                                  |

| Local-Ground-<br>Offset Adjust | Set by the user to enable local-ground-offset adjust function. Cleared by the user to disable local-ground-offset adjust function (default). Refer to the Design Features section for further details.                                                                                                                 |

| D0/D1 Direction                | Set by the user to enable D0/D1 as outputs. Cleared by the user to enable D0/D1 as inputs (default). Refer to the Design Features section for further details.                                                                                                                                                         |

| D0/D1 Value                    | I/O Port Status Bits. Logic values written to these locations determine the logic outputs on the D0 and D1 pins when configured as outputs. These bits indicate the status of the D0 and D1 pins when the I/O port is active as an input. When enabled as inputs, these bits are don't cares during a write operation. |

| SDO Disable                    | Set by the user to disable the SDO output. Cleared by the user to enable the SDO output (default).                                                                                                                                                                                                                     |

| CLR                            | Addressing this function resets the DAC outputs to 0 V in twos complement mode and negative full scale in binary mode.                                                                                                                                                                                                 |

| LOAD                           | Addressing this function updates the DAC registers and consequently the analog outputs.                                                                                                                                                                                                                                |

#### **DATA REGISTER**

The data register is addressed by setting the three REG bits to 010. The DAC address bits select with which DAC channel the data transfer is to take place (see Table 9). Position the data bits from DB15 to DB0, as shown in Table 12.

#### Table 12. Programming the Data Register Bit Map

| REG2 | REG1 | REG0 | A2 | A1         | A0 | DB15:DB0        |

|------|------|------|----|------------|----|-----------------|

| 0    | 1    | 0    | D  | AC Address | 5  | 16-Bit DAC Data |

#### **COARSE GAIN REGISTER**

The coarse gain register is addressed by setting the three REG bits to 011. The DAC address bits select with which DAC channel the data transfer is to take place (see Table 9). The coarse gain register is a 2-bit register and allows the user to select the output range of each DAC, as shown in Table 13 and Table 14.

#### Table 13. Programming the Coarse Gain Register Bit Map

| REG2 | REG1 | REG0 | A2 | A1         | A0 | DB15: DB2  | DB1 | DB0 |

|------|------|------|----|------------|----|------------|-----|-----|

| 0    | 1    | 1    | ۵  | DAC Addres | S  | Don't Care | CG1 | CG0 |

#### Table 14. Output Range Selection

| Output Range    | CG1 | CG0 |

|-----------------|-----|-----|

| ±10 V (Default) | 0   | 0   |

| ±10.2564 V      | 0   | 1   |

| ±10.5263 V      | 1   | 0   |

#### **FINE GAIN REGISTER**

The fine gain register is addressed by setting the three REG bits to 100. The DAC address bits select with which DAC channel the data transfer is to take place (see Table 9). The fine gain register is a 6-bit register and allows the user to adjust the gain

of each DAC channel by -32 LSBs to +31 LSBs in 1 LSB increments, as shown in Table 15 and Table 16. The adjustment is made to both the positive full-scale points and the negative full-scale points simultaneously, each point being adjusted by  $\frac{1}{2}$  of one step. The fine gain register coding is twos complement.

| Table 15 | Drogramming the   | Eina Cain   | Dogistor Bit Man |

|----------|-------------------|-------------|------------------|

| Table 15 | . Programming the | : rine Gain | Register bit Map |

| REG2    | REG1       | REG0      | A2         | A1      | AO   | DB15:DB6   | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------|------------|-----------|------------|---------|------|------------|-----|-----|-----|-----|-----|-----|

| 1       | 0          | 0         |            | DAC Add | ress | Don't Care | FG5 | FG4 | FG3 | FG2 | FG1 | FG0 |

| Table 1 | 6. AD5764  | Fine Gair | n Register | Options |      |            |     |     |     |     |     |     |

| Gain Ad | ljustment  |           |            | FG5     | FG4  | FG3        | F   | G2  | FG  | I   | FG0 |     |

| +31 LSB | s          |           |            | 0       | 1    | 1          | 1   |     | 1   |     | 1   |     |

| +30 LSB | s          |           |            | 0       | 1    | 1          | 1   |     | 1   |     | 0   |     |

|         |            |           |            |         |      |            |     | •   |     |     |     |     |

| +2 LSBs |            |           |            | 0       | 0    | 0          | 0   |     | 1   |     | 0   |     |

| +1 LSB  |            |           |            | 0       | 0    | 0          | 0   |     | 0   |     | 1   |     |

| No Adju | stment (De | fault)    |            | 0       | 0    | 0          | 0   |     | 0   |     | 0   |     |

| -1 LSB  |            |           |            | 1       | 1    | 1          | 1   |     | 1   |     | 1   |     |

| -2 LSBs |            |           |            | 1       | 1    | 1          | 1   |     | 1   |     | 0   |     |

|         |            |           |            |         |      |            |     | •   |     |     |     |     |

| -31 LSB | s          |           |            | 1       | 0    | 0          | 0   |     | 0   |     | 1   |     |

| -32 LSB | S          |           |            | 1       | 0    | 0          | 0   |     | 0   |     | 0   |     |

DB0

OF0

#### **OFFSET REGISTER**

REG1

0

REG2

1

The offset register is addressed by setting the three REG bits to 101. The DAC address bits select with which DAC channel the data transfer is to take place (see Table 9). The AD5764 offset

A2

A1

DAC Address

A0

DB15:DB8

Don't Care

Table 17. Programming the Offset Register Bit Map

register is an 8-bit register and allows the user to adjust the offset of each channel by -16 LSBs to +15.875 LSBs in increments of 1/8 LSB, as shown in Table 17 and Table 18. The offset register coding is twos complement.

DB4

OF4

DB3

OF3

DB2

OF2

DB1

OF1

| Offset Adjustment       | OF7 | OF6 | OF5 | OF4 | OF3 | OF2 | OF1 | OFO |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| +15.875 LSBs            | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| +15.75 LSBs             | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

|                         |     |     |     |     |     |     |     |     |

| +0.25 LSBs              | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| +0.125 LSBs             | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| No Adjustment (Default) | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| –0.125 LSBs             | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| –0.25 LSBs              | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

|                         |     |     |     |     |     |     |     |     |

| –15.875 LSBs            | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| -16 LSBs                | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

DB7

OF7

DB6

OF6

DB5

OF5

1

REG0

# OFFSET AND GAIN ADJUSTMENT WORKED EXAMPLE

Using the information provided in the previous section, the following worked example demonstrates how the AD5764 functions can be used to eliminate both offset and gain errors. Because the AD5764 is factory calibrated, offset and gain errors should be negligible. However, errors can be introduced by the system that the AD5764 is operating within, for example, a voltage reference value that is not equal to 5 V introduces a gain error. An output range of  $\pm 10$  V and twos complement data coding is assumed.

#### **Removing Offset Error**

The AD5764 can eliminate an offset error in the range of -4.88 mV to +4.84 mV with a step size of  $\frac{1}{6}$  of a 16-bit LSB.

Calculate the step size of the offset adjustment.

Offset Adjust Step Size =

$$\frac{20}{2^{16} \times 8}$$

= 38.14 µV

Measure the offset error by programming 0x0000 to the data register and measuring the resulting output voltage, for this example the measured value is  $614 \mu$ V.

Calculate the number of offset adjustment steps that this value represents.

Number of Steps =

$$\frac{Measured Offset Value}{Offset Step Size}$$

=  $\frac{614 \,\mu V}{38.14 \,\mu V}$  = 16 Steps

The offset error measured is positive, therefore, a negative adjustment of 16 steps is required. The offset register is 8 bits wide and the coding is twos complement. The required offset register value can be calculated as follows:

Convert adjustment value to binary: 00010000.

Convert this to a negative twos complement number by inverting all bits and adding 1: 11110000.